DC-DC Power Modules (en inglés)

Convertidores DC-DC personalizados Explore DC-DC ConvertersProductos de Encoder

Productos de sensores

Productos de Control de frecuencia

FHT3550 DC/DC ajustmódulo de potencia Buck (3.5V-40V de entrada, 1.0V-12.0V de salida)

detalles

FHT3860 DC/DC Step Down Buck Power Module (entrada 2.3V-5.5V, salida 0.5V-3.3V)

detalles

FHT4618 integrado DC/DC ajustmódulo de potencia Buck (entrada de 4.5V-24V, salida de 0.6V-5.5V)

detalles

FHT4623 DC/DC ajustmódulo de potencia del convertidor Buck (entrada 4.2V-20V, salida 0.6V-5.5V)

detalles

FHT4644 ultrafino multi-canal DC/DC Buck módulo de alimentación (entrada 4.0V ~ 15V, salida 0.8V ~ 5.5V)

detalles

FHT8027C DC/DC Buck convertidor de módulo de potencia integrado (entrada 5V-60V, salida 2.5V-24V)

detalles

FHT23030 DC/DC ajustmódulo convertidor Buck (entrada 4.5V-17V, salida 0.9V-6V)

detalles

MPPM8070 módulo de convertidor Buck ajustdc /DC (entrada 4.5V-18V, salida 0.6V-15V)

detalles

FHT4630 doble canal DC/DC ajustmódulo de convertidor Buck (entrada de 4.5V~15V, salida de 0.6V ~ 1.8V)

detalles

FHT4644H 4 canales integrados DC/DC ajustmódulo de potencia Buck (entrada 4.0V ~ 14V, salida 0.6V ~ 5.5V)

detalles

FHT4644L módulo de alimentación Buck DC/DC ajustintegrado de 4 canales (entrada 4.0V ~ 15V, salida 0.8V ~ 5.5V)

detalles

UDM3606 integrado de media tensión DC-DC Buck Step Down Power Module (entrada de 4.5V-18V, salida de 0.6V-5.5V)

detalles

UDM3610 integrado de media tensión DC-DC Buck Step Down módulo de fuente de alimentación (entrada 4.5V-18V, salida 0.6V-5.5V)

detallesRango de tensión de entrada: 4V-16V

Tensión de salida: 0,6-5,5v ajustable

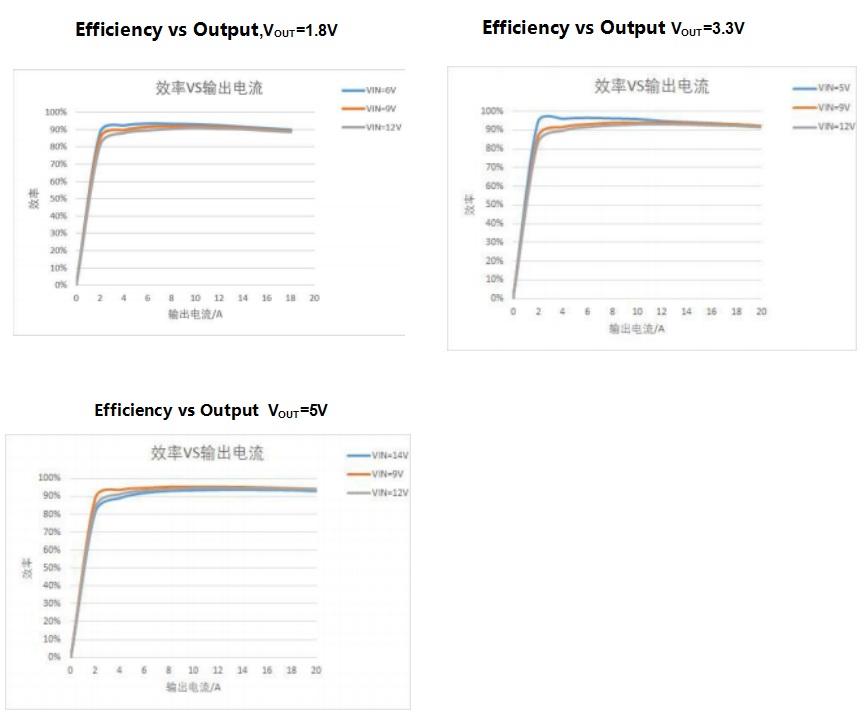

Máxima eficiencia: 95%

Coiente nominal de salida: 20un

Máxima corriente de salida: 25un

Operación en paralelo multifase: hasta 8 fases pueden ser paralelas, cel una corriente paralela máxima de hasta 200un.

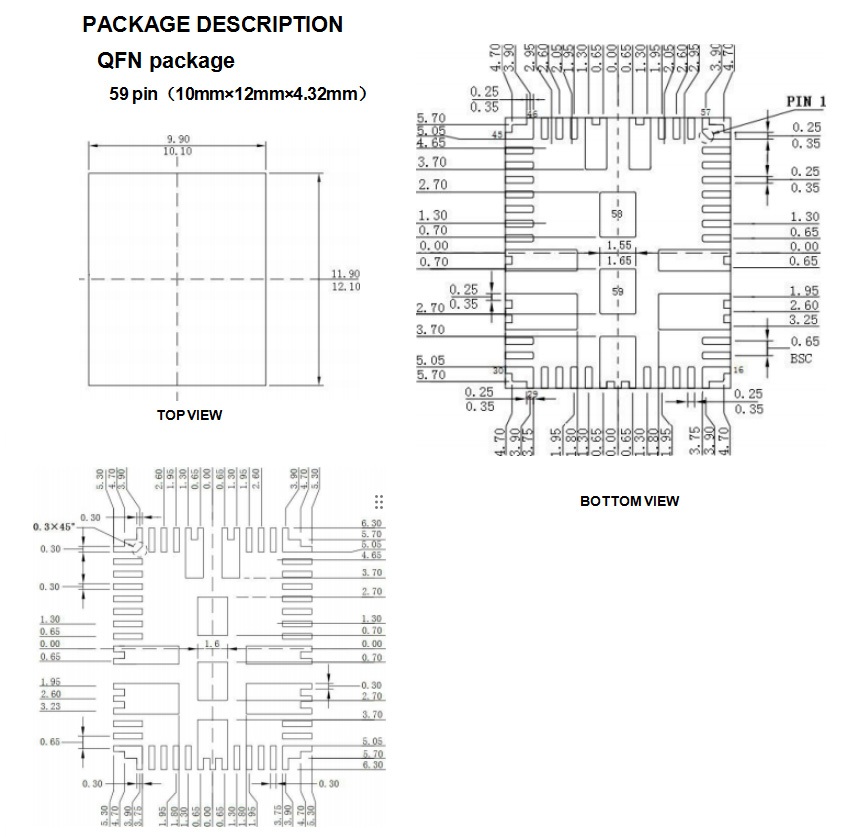

Dimensieles: 10mm i 12mm − 4.32mm(LGA)

Telecomunicacieles y redes de telecomunicacieles

Equipamiena Industrial

Servidores y sestemas informáticos

FPGA/ASIC for AI and Data Mining (en inglés)

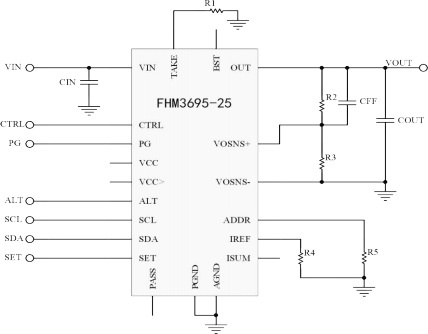

FHM 3695-25 es un módulo de potencia ampliable, totalmente integrado, encapsulde plástico cel una interfaz PMBus. FHM 3695-25 derece una solución completa de fuente de alimentación capaz de suministrar una corriente de salida máxima de hasta 25A, con una excelente regulación de la carga y una excelente regulación de la tubería. Opera eficientemente sobre un amplio rango de carga y puede ser paralelo para prpoorcionar mayores corrientes de carga.

El FHM 3695-25 utiliza el control multifase en tiempo constante (MCOT), que proporciona una respuesta transitoria ultrarrápida y una compensación de bucle simple. La interfaz PMBus ofrece la configuración del módulo y la monitorización de parámetros críticos.

FHM 3695-25 cuenta con funciones de protección integrales, incluyendo protección de sobrecorriente (OCP), protección de sobretensión (OVP), protección de subtensión (UVP), y protección de sobretemperatura (OTP). FHM 3695-25 minimiel uso de componentes externos y adopta un paquete LGA-59 (10mm×12mm×4.32mm).

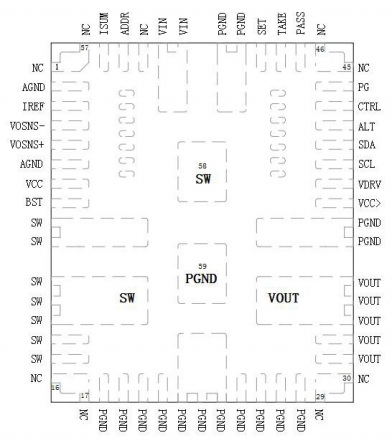

Configuración del PIN

Vista de arriba

El El Pin | Símbolo símbolo | descripción |

2,6 | AGND | Pin de señal de tierra. |

3 | IREF | Pin actual de salida de referencia de salida de referencia, mantenga este pin flotando. |

4 | - | Pin de sentido negativo de tensión de salida. Conecte directamente al GND en el lado de carga. Si no se utiliza la teledetección, acortar a GND. |

5 | + | Pin de sentido de tensión de salida positivo. Coneceste este pin al punto de sentido positivo de la tensión de salida para proporcionar tensión de retroalimentación al sistema. |

7 | VCC | Salida del LDO interno de 5V. |

8 | BST | Bootstrap pin (en inglés). Flotando. |

9-15,58 | SW | Interruptor de pin de salida. Flotando. |

31-35 | VOUT | Tensión de salida del módulo |

18-28,36,37,50,51,59 | PGND | Power ground pin (en inglés). |

38 | VCC > | Entrada de fuente de alimentación para el circuito de accion. Conecte al pin VCC (pin 7). |

39 | VDRV | Pin de fuente de alimentación para circuitos de accionamiento y control. Conecte un condensde 4.7μF a tierra. |

40 | ESL | PMBus clock pin (en inglés). |

41 | SDA | PMBus data pin. |

42 | ALT | PMBus alert pin (en inglés). |

Pin | Símbolo símbolo | descripción |

43 | CTRL | Habilitar pin. Un pin de entrada de señal utilizado para encender o apagar el módulo. ConecCTRL a VCC a través de una resistencia pullup. No deje esta clavija flotando. |

44 | PG | Pin de indicación de estado de salida. Indica un alto nivel a través de una resistencia pullup si el voltade salida está dentro del rango especificado. |

47 | PASS | Pin de señal de control de lazo de tensión. |

48 | TAKE | Definición de la dirección de fase pin. Conecte una resistencia a tierra para establecer la fase PWM. |

49 | El conjunto | Pin de sincronización. Conecte los pines de conjunto de todos los módulos que operan en paralelo juntos para sincronila sincronización PWM. |

52,53 | VIN | Pin de entrada de tensión de la fuente de alimentación. |

55 | ADDR | PMBus address El conjuntoting pin (en inglés). Conecte una resistencia entre este pin y AGND para ajustar el modul's dirección. |

56 | Suma suma | Compartir pin actual. Para aplicaciones monofásicas, mantenga este pin flotante; para Aplicaciones multifase, conectar los pines ISUM de todas las fases juntos. |

1,16,17,29, 30,45,46,54,57 | NC | vacío |

Máximo máximo absoluto Las calificaciones | condiciones | Mínimo mínimo | Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal Nominal | máximo | unidad |

VIN | 20 | V | |||

VOUT | 5.5 | V | |||

Vcc | -0.3 | 5.5 | V | ||

VSW(DC) | -0.3 | 20 | V | ||

VSW(25ns) | -0.3 | 25 | V | ||

Vbst(DC) | -0.3 | 23.5 | V | ||

Todos los demás pines | -0.3 | 5.5 | V | ||

Temperatura de almacenamiento | — 55 | +125 | i | ||

Características de entrada | condiciones | Mínimo mínimo | Nominal | máximo | unidad |

Rango de tensión de entrada | 4 | 16 | V | ||

Umbral de bloqueo de subtensión VCC (en aumento) | 2.9 | 3 | 3.1 | V | |

Umbral de bloqueo de subtensión VCC (caída) | 2.7 | V |

Corriente de entrada a plena carga | VIN=12V,VOUT=5V,IOUT=20A | 8.8 | A | ||

Corriente de entrada en vacío | VIN=12V,VOUT=1.8V,IOUT=0A CCM | 60 | mA | ||

Corriente de entrada cuando está apagado | ON/OFF=OFF | 2 | 4 | mA | |

Características de entrada | condiciones | Mínimo mínimo | Nominal | máximo | unidad |

Frecuencia de conmutación | 600 | A KHz | |||

eficiencia | 95 | % | |||

funcionalidad | condiciones | Mínimo mínimo | Nominal | máximo | unidad |

CTRL habilitar la tensión (subida) | VCC-1 | V | |||

CTRL habilitar la tensión (caída) | 1.2 | V | |||

Tiempo de inicio suave (TSS) | 61h[2:0] = 3b '001 | 2 | M s | ||

Tiempo de inicio programable mínimo (tss_min) | 61h[2:0] = 3b '000 |

1 |

M s | ||

Tiempo de inicio programable máximo (tss_max) |

16 |

M s | |||

PG de alto umbral (subida de PGVth) | FB from low to High, configuración por defecto (D9h[10] 2b '01) |

0,95 |

VREF | ||

PG umbral bajo (subida) (PGVth_Lo_Rise) | FB from low to High, configuración por defecto (D4h[10] = 2b '00) |

1.15 |

VREF | ||

PG umbral bajo (caída) (PGVth_Lo_Fall) | FB from low to High, configuración por defecto (D9h[3:2] (2b '10) |

0,8 |

VREF |

características | condiciones | Mínimo mínimo | Nominal | máximo | unidad |

Tensión de salida | 0,6 | 5.5 | V | ||

Regulación de línea | VOUT=3.3V,IOUT=20A | 1.2 | 1.5 | % | |

Regulación de carga | VIN=5V,VOUT=3.3V | 2.1 | 2.3 | % | |

Onduly ruido | VIN=12V,VOUT=1.8V,IOUT=20A | 21 | En En mV | ||

Respuesta a la carga dinámica | 50-100% de carga Di /dt=2.5A/μs | 70 | mV | ||

Límite de corriente de salida (corriente del valle del Inductor) | D7h = 0x14 | 27 | 30 | 33 A | A |

Características estructurales | condiciones | Mínimo mínimo | Nominal | máximo | unidad |

dimensiones | 10 × 12 ×4.32 | mm | |||

peso | 3 | g | |||

Adaptación ambiental | condiciones | Mínimo mínimo | Nominal | máximo | unidad |

Temperatura de funcionamiento (temperatura de Unión de funcionamiento) | -40 | 125 | i | ||

Almacenamiento de alta temperatura (temperatura ambiente) | +125 +125 , 48h | 125 | i | ||

Funcionamiento a alta temperatura (temperatura ambiente) | +85i , 24 horas; Entrada a baja tensión, tensión estándar, Y alta tensión durante 8 horas cada uno; VIN =60V ,VOUT =12V IOUT=2.4A |

85 | i | ||

Almacenamiento a baja temperatura (temperatura ambiente) | — 55i , 24 horas | — 55 | i | ||

Funcionamiento a baja temperatura (temperatura ambiente) | -40i , 24 horas; Entrada a baja tensión, tensión estándar, Y alta tensión durante 8 horas cada uno | -40 | ℃ | ||

Calor húmedo | Alta temperatura y Fase de alta humedad :60℃ , 95%; Fase de baja temperatura y alta humedad :30℃ , 95%; Ciclo de 10 ciclos, cada ciclo dura 24 horas. |

30 |

60 | ℃ | |

Choque térmico choque térmico | Alta temperatura a 125°C y baja temperatura a -55°C, Con cada temperatura que dura una hora formando un ciclo. Toda la prueba consta de 32 ciclos. | -55 | 125 | ℃ |

Nota:

Esfuerzos por encima de los valores que figuran en los "valores límite" Sección puede causar daños permanentes en el dispositivo. La exposición prolongada a cualquiera de las clasificaciones máximas absolutas puede afectar la confiabilidad y vida útil del dispositivo.

El FHM 3695-25 es una solución de potencia totalmente integrada que viene en un paquete LGA de 10×12× 4,32 mm, proporcionando una corriente de salida nominal de 20A y una corriente de salida pico de hasta 25A. Para aplicaciones que requieren corrientes superiores a 25A, se puede utilizar una conexión paralela para proporcionar corrientes de salida más altas.

El FHM 3695-25 emplea un método de control constante en tiempo (COT), lo que resulta en una respuesta transitoria rápida. La compensación de la pendiente interna garantiza un funcionamiento estable en aplicaciones que utilizan condensadores de salida de cerámica ESR cero.

En una configuración multifase, una fase maestra y hasta siete fases esclavestán conectadas en paralelo. Todas las fases distribuyen por igual la corriente de salida. Un circuito de aplicación típico ejemplifica la configuración paralela de dos dispositivos FHM 3695-25. En una instalación multifase, el pasador de toma de la fase maestra tiene que ser tirado a tierra a través de una resistencia. El FHM 3695-25 detecta su configuración master/slave monitorizando el estado de la toma durante el proceso de arranque.

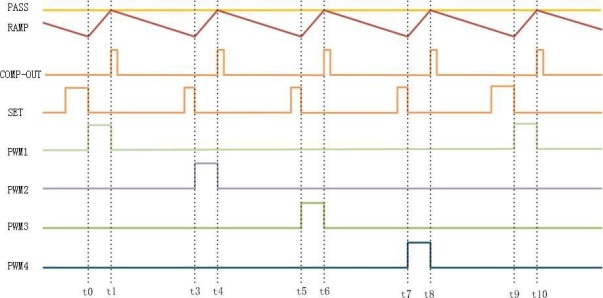

MCOT operación - fase maestra

• recibe comandos de escritura y lectura del host a través de la interfaz PMBus

• genera la señal de SET

• maneja el arranque, apagado y todas las operaciones de protección

• monitoriza las alertas de fallos de las fases esclavmediante el pin PG

• genera el primer pulso de encendido

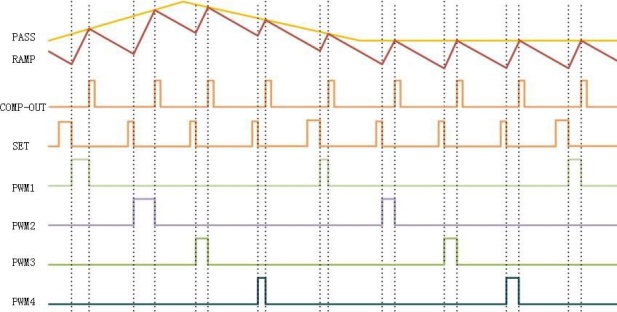

• genera pulsos al recibir señales de funcionamiento y ajuste

• ajusta dinámicamente su tiempo para asegurar un reparto de corriente equitativo

La fase esclrealiza las siguientes funciones:

• recibe comandos de escritura desde el host a través de la interfaz PMBus

• recibe la señal de SET de la fase maestra

• envía alertas de fallos OV/UV/OT a través del pin PG

• inicia los pulsos al recibir las señales CTRL y SET

• ajusta dinámicamente su tiempo para asegurar un reparto de corriente equitativo basado en la corriente por fase y la corriente total relativa a su propia fase

El FHM 3695-25 se beneficia del control MCOT, lo que permite una respuesta transitoria de carga extremadamente rápida. Durante los transitorios de carga, las señales de ajuste se generan con más frecuencia en comparación con las condiciones de estado estacionario. Por lo tanto, la energía se entrega a la carga a una tasa más alta, minimizando la desviación de salida durante los transitorios de carga. Para el FHM 3695-25, los pulsos de ajuste se generan con un El intervaloo mínimo de 50ns, lo que significa que la siguiente fase se puede activar tan rápido como 50ns después de la anterior.

Configuración de fase paralela multifase

Cuando se aplica el FHM3695 en una configuración paralela multifase, la configuración de fase debe lograrse mediante la conexión de un valor de resistencia correspondiente del pin ADDPH a tierra, lo que permite el escalonde fase y la distribución de corriente.

Secuencia de fase | R_ADDPH(kΩ) |

1 | 5 |

2 | 15 |

3 | 25 |

4 | 37 |

5 | 52 |

6 | 70 |

7 | 95 |

8 | 125 |

Diagrama de tiempo de funcionamiento de cuatro fases (estado estacion)

Diagrama de tiempo de funcionamiento de cuatro fases (estado dinámico)

Selección del modo de trabajo

El FHM 3695-25 ofrece un CCM forzado (modo de corriente constante) y modo de salto de frecuencia de trabajo bajo condiciones de carga ligera, que se puede configurar a través de PMBus con comandos como se muestra en la tabla

Cuadro 1 MFR_CTRL_OPS(D2h)

Bits | nombre | Por defecto | descripción |

[7:3] | Reservado. | 00000 | |

[0] | SKIP_CCM | 1 | 0: modo de salto de frecuencia 1: modo forzado CCM |

Frecuencia de funcionamiento

La frecuencia de funcionamiento del FHM 3695-25 es de 600KHz.

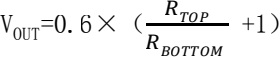

Ajuste de la tensión de salida

El voltade salida del módulo puede ser ajustado por la resistencia pullup RTOP Entre VOSNS+ y VOUT, y la resistencia pulldown RBOTTOM Entre VOSNS+ y VOSNS-. La fórmula de cálculo de referencia es la siguiente:

Inicio suave

El tiempo de inicio suave (SS) se puede programar a través de PMBus. El tiempo por defecto es 2ms.

Antes de la puesta en marcha

La FHM 3695-25 garantiza un arranque ascendente monotónico cuando la tensión de salida está ses. Si la tensión de salida se presesa a una cierta tensión durante el arranque, tanto los interruptde lado alto y lado bajo se desactivhasta que la tensión de salida sensed en el pin vos+ cae por debajo de la tensión de referencia interna.

Detección de corriente y protección de sobrecorriente (OCP)

El FHM3695-25 cuenta con detección de corriente en chip y un umbral de límite de corriente positivo programable.

El FHM 3695-25 proporciona dos límites de corriente del valle del inductor (establecidos por el registro D7h).

Protección de la sobrecorriente del valle del Inductor (D7h)

Durante el estado de conducción LS-FET, la corriente del inductor se detecta y se monitorea ciclo por ciclo. El HS-FET sólo se le permite conducir si no se detecta un exceso de corriente durante el estado de conducción LS-FET. Si se detectan 31 condiciones OC consecutivas, se activa el OCP.

En el caso de una condición de sobrecorriente o cortocircuito de salida, si la tensión de salida cae por debajo del umbral de protección de subtensión (UVP), el FHM 3695-25 entra inmediatamente en modo de protección de sobrecorriente.

Después de activar el OCP, si el FHM3695-25 entra en el modo hipo o en el modo latch-fuera depende de la configuración del registro. Cabe señalar que una vez apagado, volver a activar el FHM 3695-25 requiere reiniciar Vcc o CTRL.

El límite de sobrecorriente del valle del inductor se puede programar mediante el registro D7h, que establece el límite de corriente del valle del inductor para cada fase, tanto para operaciones monofásicas como multifásicas. Los comandos se muestran en la tabla 3.

Table3 MFR_OC_PHASE_SET(D7h)

Bits | nombre | Por defecto | descripción |

[7:5] | Reservado. | 000 | |

[4:0] | OC_limit | 10100 | Límite actual. 1.5A/LSB, [00000] = 0A. |

Límite de corriente del Inductor de fase negativa

Cuando la corriente detectada por el LS-FET cae por debajo del límite de corriente de fase negativa establecido por el registro D5h[2], el dispositivo apagará su LS-FET por un período de tiempo para limitar la corriente de carga. El período se puede fijar vía el registro D5h[3]. Los comandos se muestran en la tabla 4.

Table4 MFR_OVP_NOCP_SET (D5h)

Bits | nombre | Por defecto | descripción |

[7:4] | Reservado. | 0000 | |

[3] | DELAY_NOCP(D400) | 0 | 0: 100ns de retraso después de NOCP 1:200ns retraso después de NOCP |

[2] |

NOCP |

0 | 0: establece NOCP a 10a 1: Set NOCP to -15A |

Protección contra sobretensión (OVP)

El FHM 3695-25 monitla el voltade salida a través del pin VOSNS+ en el separador de resistencia para detectar condiciones de sobretensión. El valor de protección de sobretensión se puede ajustar mediante el registro D4h, con los comandos específicos que se muestran en la tabla 5.

Table5 MFR_VOUT_OVP_FAULT_LIMIT (D4h)

Bits | nombre | Por defecto | descripción |

[7:4] | Reservado. | 0000 | |

[3:2] |

OV_EXIT_TH |

00 | Establecer la salida Umbral para el OVP 00: 10% * VREF 01: 50% * VREF 10 80% * VREF 11: 102,5% * VREF |

[1:0] |

OV_ENTRY_TH |

00 | Establecer el umbral de entrada para OVP 00: 115% *VREF 01: 120% *VREF 10 125% *VREF 11: 130% *VREF |

Protección bajo tensión (UVP)

El FHM 3695-25 monitla el voltade salida a través del pin de VOSNS+ para detectar condiciones de bajo volta. Si los vos+

El voltacae por debajo del umbral UVP (establecido a través del registro D9h, como se muestra en la tabla 6), el UVP se activa. Al activar el UVP, el FHM 3695-25 entrará en el modo hipo o en el modo latch-fuera, dependiendo de la configuración del PMBus. Tenga en cuenta que una vez que el dispositivo está apagado, para volver a activar el FHM 3695-25, es necesario reiniciar Vcc o CTRL.

Cuadro 6 MFR_UVP_PGOOD_ON_LIMIT (D9h)

Bits | nombre | Por defecto | descripción |

[7:4] | Reservado. | 0000 | |

[3:2] |

uv_o |

00 | Establecer el umbral de UVP. Cuando el voltafb cae por debajo del nivel uv_o, UVP Se activa. 00: 69% * VREF 01: El 74% * VREF 10 79% * VREF 11: 84% * VREF |

Modo sumidero de salida (OSM)

Cuando la tensión de salida excede la tensión de referencia en más del 5%, pero permanece por debajo del umbral OVP, el FHM 3695-25 entra en OSM. Al activar el OSM, el FHM 3695-25 opera en modo forzado CCM. El FHM 3695-25 sale del modo OSM cuando el HS-FET se reactiva. Esta característica puede ser activada o desactiva través del registro EAh[9], con las instrucciones proporcionadas en la tabla 7.

Cuadro 7 MFR_CTRL(EAh)

Bits | nombre | Por defecto | descripción |

[15:1 1] | Reservado. | 00000 | |

[9] |

OSM |

0 | Activar o desactivar la función OSM. 0: activar 1: deshabilitar |

Protección contra la sobretemperatura (OTP)

El FHM 3695-25 controla la temperatura de Unión. Si la temperatura de la Unión excede el umbral, el convertientrará en el modo hipo o en el modo latch-fuera, dependiendo de la selección de PMBus. Tenga en cuenta que una vez apagado, para volver a activar el MPM3695-25 (asumiendo it' un error tipopara FHM 3695-25), es necesario reiniciar Vcc o CTRL.

El umbral de temperatura de Unión se puede ajustar mediante el registro 4Fh, con instrucciones específicas en la tabla 8. El valor no está firmado, con 1 LSB que equivale a 1 °C, y el valor por defecto es 0x009B (155 °C).

Tabla 8 OT_FAULT_LIMIT (en inglés) (en inglés) (en inglés) (4Fh)

Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

acceso | r | |||||||

función | C/LSB | |||||||

Por defecto valor | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | R /w | |||||||

función | C/LSB | |||||||

Por defecto valor | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

Poder bueno (PG)

El FHM 3695-25 cuenta con un pin de señal de drenaje abierto para determinar el estado de potencia buena (PG). El pin de PG puede ser configurado como un pin de sólo salida o como un pin de entrada y salida vía bit [0] del registro MRF_CTRL_COMP (D0h), como se muestra en la tabla de instrucciones 9. Para configuraciones monofásicas, el pin PG debe ser configurado únicamente como un pin de salida. Para operaciones multifase, el pin de PG debe ser configurado como un pin de entrada y salida para detectar fallas en las fases. Es necesario tirar del pin PG hasta VCC o la fuente de voltaa través de una resistencia pull-up (típicamente 100kΩ).

Una vez que el voltade entrada se aplica al FHM 3695-25, el pin de PG se baja. Cuando la tensión VOSNS+ alcanza el umbral establecido en el registro D9h (como se muestra en la tabla de instrucciones 10) y después del retardo establecido en el registro D1h (como se muestra en la tabla de instrucciones 11), el pin PG se tira alto.

En caso de aver, el pin de PG se bloquea bajo y activa funciones de protección relacionadas (como UV, OV, OT, UVLO, etc.). Una vez que el pin de PG está trabched bajo, no se puede tirar alto otra vez a menos que un nuevo comienzo suave se inicie.

Tabla 9 MFR_CTRL_COMP (D0h)

Bits | nombre | Por defecto | descripción |

[7:5] | Reservado. | 0000 | |

[0] | Fallo del esclavo detección | 1 | 0: habilitar la detección de fallas de fase 1: deshabilitar la detección de fallos de fase |

Tabla 10 MFR_UVP_PGOOD_ON_LIMIT (D9h)

Bits | nombre | Por defecto | descripción |

[7:4] | Reservado. | 0000 | |

[1:0] |

PG_ON |

00 | Establezca el umbral FB para que PG se tire alto durante el arranque suave. Una vez que el FB alcanza el umbral, el PG se tira de alto después de un retraso establecido por D1[5:2]. 00: 90% * VREF 01: 92,5% * VREF 10: 95% * VREF 11: 97,5% * VREF |

Tabla 11 MFR_CTRL_VOUT (D1h)

Bits | nombre | Por defecto | descripción |

[7] | Reservado. | 0 | |

[5:2] | PG retraso |

0000 | Establecer el PG pull-up tiempo después de que el inicio suave se ha completado. |

Bits | nombre | Por defecto | descripción |

[7:5] | Reservado. | 0000 | |

[0] | Fallo del esclavo detección | 1 | 0: habilitar la detección de fallas de fase 1: deshabilitar la detección de fallos de fase |

El diseño

La disposición del PCB es crucial para la estabilidad del módulo de potencia#39 y 39 Para lograr un rendimiento óptimo, por favor siga estas pautas:

1. Coloque los condensadores de entrada de cerámica lo más cerca posible de los pines VIN y PGND. Utilice grandes pours de cobre para VIN y PGND para minimizar la impedparásito y reducir la resistencia térmica.

2. Añadir vías VIN a al menos 3mm de distancia del dispositivo para minimizar el ruido causado por las corrientes de pulso de entrada.

3. Conecte AGND y PGND en un solo punto.

4. Coloque suficientes vías PGND de salida cerca del pin PGND para minimizar la impedparasiy la resistencia térmica.

5. Mantenga el ISUM trace lo más corto posible. En configuraciones multifase, la traza de ISUM debe mantenerse lejos de la zona de vertido de cobre VIN. Evite usar el sistema de información de tráfico tanto como sea posible.

6. Evite los rastros de señales de enrutamiento directamente debajo de las almohadillas SW a menos que la capa PGND se utilice para proporcionar blindaje.

Diseño de PCB recomendado

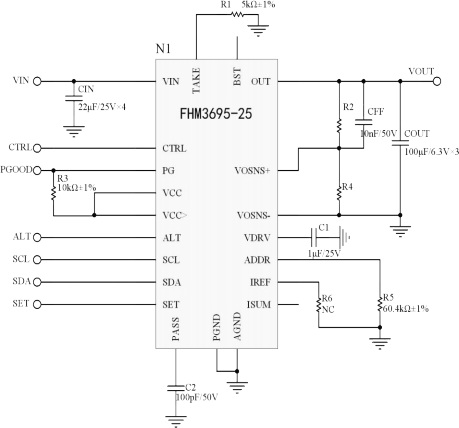

Circuito típico: aplicación monofásica

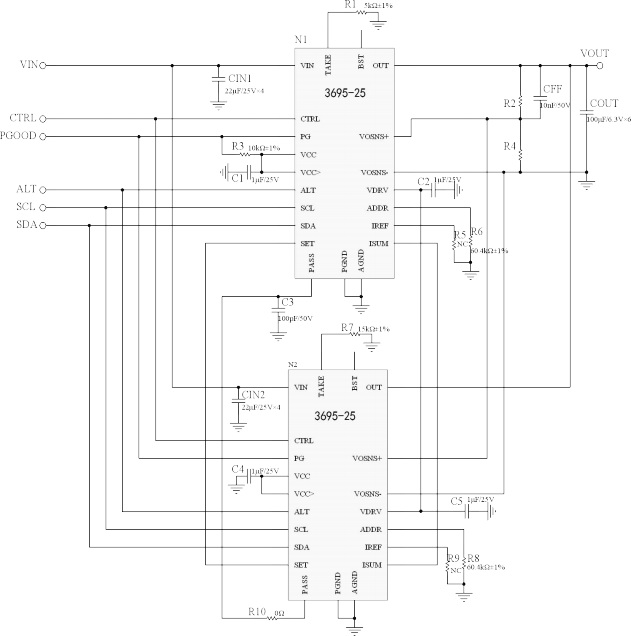

Circuito típico: aplicación en paralelo bifásico

Interfaz de serie de PMBUS

PMBus Serial Interface Explanation (en inglés)

El Power Management Bus (PMBus) es una interfaz serial bidireccional de dos hilos que comprende una línea de datos (SDA) y una línea de reloj (SCL). Cuando las líneas son "idle," Son arrastrhasta el voltadel bus por una fuente externa. Cuando se conecta a las líneas, el dispositivo maestro genera el

SCL y la dirección del dispositivo, y orquesta la secuencia de comunicación.

Opera basado en los principios I2C. La interfaz FHM 3695-25 sirve como esclavo de PMBus, soporttanto el modo estándar (100kHz) y modos rápidos (400kHz y 1MHz). La interfaz PMBus añade flexibilidad a las soluciones de fuente de alimentación.

Dirección del dispositivo

Para gestionar múltiples dispositivos FHM 3695-25 a través del mismo PMBus, utilice el pin ADDR para programar la dirección del dispositivo para cada FHM 3695-25. El ADDR pin tiene un flujo de salida actual de 10μ a. Conecte una resistencia entre el pin ADDR y AGND para ajustar el voltaaddr. La dirección PMBus se establece mediante la conversión de la tensión del pin utilizando un ADC interno. El ADDR pin puede configurar hasta 16 direcciones únicas. Adicionalmente, el registro MFR_ADDR_PMBUS (D3h) puede ser usado para establecer la dirección de PMBus digitalmente.

Una vez que se selecciona una dirección, cada dispositivo debe hacerlo

Tener una dirección única durante el funcionamiento normal.

La tabla 12 muestra la relación entre los valores de resistor ADDR y las direcciones PMBus.

Tbale12 PMBUS Address Setting (en inglés)

Cuadro 12 PMBUS

R_ADD T(kΩ) | Dirección de esclavo (R_ISET=60.4kΩ) | Dirección de esclavo (R_ISET=180kΩ) |

5 | 30h | 40h |

15 | 31h | 41h |

25 | 32h | 42h. |

37 | 33h | 43h |

52 | 34h | 44h |

70 | 35h | 45h |

95 | 36h | 46h |

125 | 37h | 47h |

Condiciones de inicio y parada

El dispositivo maestro inicia las señales de inicio/parada para indicar el inicio y el final de la transmisión de datos PMBus. La condición de inicio se define como la señal SDA en transición de alta a baja mientras SCL es alta. La condición de parada se define como la señal SDA en transición de baja a alta mientras SCL es alta.

El dispositivo maestro genera el reloj SCL y envía la dirección del dispositivo y el bit de dirección de lectura/escritura R/W en la línea SDA. Los datos se transmiten en la línea de SDA en octetos de 8 bits. Cada byte de datos es seguido por un bit de reconocimiento.

Tiempo de actualización de PMBus

Al actualizar el FHM 3695-25, se requiere una condición de inicio, una dirección PMBus válida, un byte de dirección de registro, y bytes de datos para una actualización de un solo paquete. Después de recibir cada byte, el FHM 3695-25 reconoce tirando de la línea SDA baja durante el alto nivel de un solo pulso de reloj. Una dirección PMBus válida selecciona el FHM 3695-25 para la comunicación. El FHM 3695-25 realiza la actualización en el borde de caída del byte LSB (least significant byte).

Comprobación de errores de paquetes (PEC)

La interfaz FHM 3695-25 PMBus soporta el uso de un byte de comprobación de errores de paquetes (PEC). El PEC byte es enviado por el FHM 3695-25 durante una operación de lectura o transmitido por el bus master al FHM 3695-25 durante una operación de escritura.

El bus master o el FHM 3695-25 utiliza el byte PEC para detectar errores durante la comunicación de bus, dependiendo de si se trata de una operación de lectura o escritura. Si el maestro determina que el PEC byte leído durante una operación de lectura es incorrecto, puede decidir reintentar la lectura. Si el FHM 3695-25 determina que el byte PEC enviado durante una operación de escritura es incorrecto, ignora el comando (no lo ejecuta) y establece una bandera de estado. En comandos de grupo, el maestro puede elegir enviar o no enviar un PEC byte como parte del mensaje al FHM 3695-25.

Dirección de respuesta de la alarma PMBus (ARA)

La PMBus Alarm Response Address (ARA) es una dirección especial que el bus master puede usar para localizar cualquier dispositivo que necesite comunicarse con él. El master normalmente utiliza pines de interrupción de hardware para monitorizar los pines de alerta PMBus de muchos dispositivos. Cuando el maestro es interrumpido, envía un mensaje en el bus usando los bytes de recepción PMBus o bytes recibidos con el protocolo PEC.

La dirección especial utilizada por el maestro es 0x0C. Cualquier dispositivo con una señal de alerta PMBus devuelve su propia dirección de 7 bits como los 7 bits más significativos (MSBs) de un byte de datos. El bit menos significativo (LSB) no se usa y puede ser 1 o 0. El maestro lee la dirección del dispositivo desde el byte de datos recibido y luego procede a manejar la condición de alerta.

Varios dispositivos pueden tener una señal de alerta PMBus válida e intentar comunicarse con el master. En este caso, el dispositivo con la dirección más baja toma el control del bus y envía con éxito su dirección al maestro. El dispositivo exitoso luego desactiva su señal de alerta PMBus. Si el maestro encuentra que la señal de alerta PMBus permanece baja, continuará leyendo direcciones hasta que todos los dispositivos que necesitan comunicarse con él hayan enviado con éxito sus direcciones

funcionamiento (01h)

La operación es un registro paginado. El comando de operación se utiliza para girar el converter&#Salida on/fuera de 39;s y para controlar la entrada del pin de CTRL. También se utiliza para ajustar el límite superior o inferior de la tensión de salida. La unidad permanece en el modo ordenado hasta que un comando de operación posterior o un cambio en el estado de CTRL pin instrual convertipara cambiar a otro modo. Este comando de operación también se utiliza para volver a habilitar el convertidespués de que se ha apagado debido a un gatide fallo. Escribir un comando OFF después de un comando ON borrará todos los fallos. Sin embargo, simplemente escribiendo un comando ON después de un apagado provocado por un fallo no borrará los registros de fallos. El valor por defecto es 0x80.

comando | funcionamiento | |||||||

paramato formatoo formatoo formatoo formatoo formatoo formatoo formatoo formatoo formatoo formatoo formatoo formato | Sin firmar binay | |||||||

Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w |

función | x | x | ||||||

Valor por defecto | 1 | 0 | 0 | 0 | 0 | 0 | x | x |

Bit[7:6] | Bit[5:4] | Bit[3:2] | Bit[1:0] | Encendido/apagado | Margen margen margen estado | 01h |

00 | XX | XX | XX | inmediato off | N/A | 0x00 |

01 | XX | XX | XX | inmediato off | N/A | 0x60 |

10 | 00 | XX | XX | on | off | 0x80 |

10 | 01 | 01 | XX | on | Margen bajo ( Culpa» | 0x94 |

10 | 01 | 10 | XX | on | Margen bajo (acto En caso de culpa) | 0x98 |

10 | 10 | 01 | XX | on | Margen margen margen alto (ignorar la culpa) | 0xA4 |

10 | 10 | 10 | XX | on | Margen margen margen alto (actuar sobre la falta) | 0xA8 |

ON_OFF_CONFIG (02h)

El comando ON_OFF_CONFIG configura la entrada de CTRL pin y establece la combinación de comandos PMBus necesarios para encender y apagar el converti. El valor por defecto de esta orden es 0x16.

comando | funcionamiento | |||||||

paramat | Sin firmar binay | |||||||

Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | r | r | r | R /w | R /w | R /w | R /w | R /w |

función | X | X | X | on | op | ctrl | pol_ctrl | retraso |

Valor por defecto | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 |

CLEAR_FAULTS (en inglés). (03h)

El comando CLEAR_FAULTS se utiliza para restablecer todos los indicadores de alarma y fallos almacenados.

capacidad (19h)

El comando capacidad devuelve información sobre las características de PMBus soportadas por el FHM 3695-25. Este comando se lee usando el protocolo de lectura de bytes PMBus. El valor por defecto de este comando es 0xB0.

comando | CAPABILITY | |||||||

Format | Sin firmar binay | |||||||

Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | r | r | r | r | r | r | r | r |

función | PEC | Max.bus velocidad | alerta | x | x | x | x | |

Valor por defecto | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

PEC supported, Max speed 1MHz, compatible PMBusTM alert y ARA. | ||||||||

Bit[6:5] | significado | |

0 | 0 | La velocidad máxima de bus soportada es de 100kHz. |

0 | 1 | La máxima velocidad de bus soportada es 1MHz. |

1 | 0 | Máximo apoyo La velocidad del bus es de 400kHz. |

1 | 1 | Reservado. |

VOUT_MODE (20h)

El comando VOUT_MODE se utiliza para ordenar y leer el voltade salida. Los tres bits más significativos se utilizan para determinar el formato de datos (con el FHM 3695-25 sólo soporta el formato directo), y los cinco bits restantes representan el exponente utilizado en los comandos de lectura/escritura de voltade salida. El valor por defecto de este comando es 0x40.

VOUT_COMMAND (21h)

El VOUT_COMMAND establece el voltade salida del FHM 3695-25. El valor no está firmado y tiene una resolución de 1 LSB = 2 mV. El valor por defecto de este comando es 0x0258, que corresponde a 1.2V.

comando | VOUT_COMMAND | |||||||||||||||

Format | directo | |||||||||||||||

Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | r | r | r | r | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w |

función | X | |||||||||||||||

Por defecto valor | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 |

VOUT_MAX (24h)

El comando VOUT_MAX establece el límite superior del converter&#Tensión de salida de 39;s, independientemente de otros comandos o combinaciones. El propósito de este comando es evitar que los usuarios accidentajuste la tensión de salida a un nivel excesivamente alto que exceda el device's máxima tolerancia de tensión, no sólo el rango de protección de sobretensión. El valor no está firmado y tiene una resolución de 1 LSB = 2 mV. El valor por defecto para este comando es 0x0ABE, que corresponde a 5.5V.

comando | VOUT_MAX | |||||||||||||||

Format | directo | |||||||||||||||

Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | r | r | r | r | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w |

función | X |

VOUT_SCALE_LOOP (29h)

El VOUT_SCALE_LOOP establece la relación de divide de resistencia de retroalimentación, que es igual a VOSNS+/VOUT. Independientemente de si se utiliza un divide resistencia de retroalimentación externo o interno, VOUT_SCALE_LOOP debe coincidir con el divide resistencia de retroalimentación real que está siendo utilizado. El valor es sin signo y tiene una resolución de 1 LSB = 0.001. El valor por defecto de este comando es 0x01F4, que corresponde a 0.5.

OT_FAULT_LIMIT (4Fh)

OT_FAULT_LIMIT (4Fh)

El comando OT_FAULT_LIMIT se utiliza para configurar o leer el umbral para la detección de fallos de sobretemperatura. Si la temperatura medida supera este valor, se activará la protección contra la sobretemperatura. El valor no está firmado y tiene una resolución de 1 LSB = 1°C. El valor por defecto para este comando es 0x009B, que corresponde a 155°C.

comando | OT_FAULT_LIMIT | |||||||||||||||

Format | directo | |||||||||||||||

Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | r | r | r | r | r | r | r | r | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w |

función | X | 1. C/LSB | ||||||||||||||

Por defecto valor | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

OT_WARN_LIMIT (en inglés) (en inglés) (51h)

El OT_WARN_LIMIT se utiliza para configurar o leer el umbral para la detección de advertencia de sobretemperatura. El valor no está firmado y tiene una resolución de 1 LSB = 1°C. El valor por defecto para este comando es 0x0091, que corresponde a 145°C.

comando | OT_WARN_LIMIT | |||||||||||||||

Format | directo | |||||||||||||||

Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | r | r | r | r | r | r | r | r | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w |

función | X | 1. C/LSB | ||||||||||||||

Por defecto valor | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

VIN_OV_FAULT_LIMIT (55h)

El comando VIN_OV_FAULT_LIMIT se utiliza para configurar o leer el umbral para la detección de fallos de sobretensión de entrada. El valor no está firmado y tiene una resolución de 1 LSB = 500 mV. El valor por defecto de este comando es 0x0021, que corresponde a 16.5V. El valor fijado no debe exceder 18V.

comando | VIN_OV_FAULT_LIMIT | |||||||||||||||

Format | directo | |||||||||||||||

Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | r | r | r | r | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w |

función | x | 500mV/LSB | ||||||||||||||

Por defecto valor | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

VIN_OV_WARN_LIMIT (57h)

El comando VIN_OV_WARN_LIMIT se utiliza para configurar o leer el umbral para la detección de advertencia de sobretensión de entrada. El valor no está firmado y tiene una resolución de 1 LSB = 500 mV. El valor por defecto de este comando es 0x0021, que corresponde a 16.5V. El valor máximo no debe exceder 18V.

comando | VIN_OV_WARN_LIMIT | |||||||||||||||

Format | directo | |||||||||||||||

Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | r | r | r | r | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w |

función | x | 500mV/LSB | ||||||||||||||

Por defecto valor | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

VIN_UV_WARN_LIMIT (58h)

El comando VIN_UV_WARN_LIMIT se utiliza para configurar o leer el umbral para la detección de advertencia de bajo voltade entrada. El valor no está firmado y tiene una resolución de 1 LSB = 250 mV. El valor por defecto de este comando es 0x0010, que corresponde a 4V. El valor mínimo no debe ser inferior a 3,3v.

comando | VIN_UV_WARN_LIMIT | |||||||||||||||

Format |

directo | |||||||||||||||

Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | r | r | r | r | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w |

función | x | 250mV/LSB | ||||||||||||||

Por defecto valor | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

TON_DELAY (60h)

Este comando es de sólo lectura, y el valor por defecto es 0x0000 (0ms).

TON_RISE (en inglés). (en inglés). (61h)

El comando TON_RISE establece el tiempo de inicio suave, en milisegundos, que se refiere al tiempo que tarda la salida en elevarse desde el inicio hasta que el voltaalcanza su punto regulado. El valor es sin signo, con 1 LSB = 1 ms. El valor por defecto es 0x0001 (2 ms), y el valor máximo es 0x0007 (16 ms).

comando | TON_RISE | |||||||||||||||

Format | directo | |||||||||||||||

Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | r | r | r | r | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w |

función | x | x | x | x | x | x | x | x | x | x | x | x | x | 1ms/LSB | ||

Por defecto valor | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

MFR_CTRL_VOUT (D1h)

Bits | nombre | acceso | comportamiento | Por defecto | descripción |

[7] | Reservado. | R /w | En vivo | 0 | |

[6] |

Vo discharge |

R /w |

En vivo |

1 | permite or desactivar el activo salida La tensión de tensión discharge cuando el FNM3695-25 is Por orden off A través CTRL or el Comando de operación. |

[5:2] | PG retraso | R /w | En vivo | 0000 | Establece el PG pull-alto time después de que el inicio suave termina. |

[1:0] |

El alcance de la FB |

R /w |

En vivo |

00 | Elige la relación divisor de tensión interna 00: Vref/FB = 1, FB = 0.4 ~ 0.672V, LSB = 2mV 01: Vref/FB = 0.5, FB = 0.4 ~ 1.344V, LSB = 2mV 10: Vref/FB = 0,25, FB = 0.7 ~ 2.688V, LSB = 2mV 11: Vref/FB = 0.125, FB = 1.3 ~ 5.376V, LSB = 2mV |

MFR_ADDR_PMBUS (D3h)

comando | MFR_ADDR_PMBUS | |||||||

Format | directo | |||||||

Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

acceso | R /w | R /w | R /w | R /w | R /w | R /w | R /w | R /w |

función | habilitar | ADDR | ||||||

Valor por defecto | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

MFR_VOUT_UV_OV_FAULT_LIMIT (en inglés) (D4h)

Bits | nombre | acceso | comportamiento | Por defecto | descripción |

[7:4] | Reservado. | 0000 | |||

[3:2] |

OV_EXIT_TH |

R /w |

En vivo |

00 | Establece la salida del OVP Umbral. 00: 10% * VREF; 01: 50% * VREF; 10: 80% * VREF; 11: 102,5% * VREF. |

[1:0] |

OV_ENTRY_TH |

R /w |

En vivo |

00 | Establece la entrada OVP Umbral. 00: 115% *VREF; 01: 120% *VREF; 10: 125% *VREF; 11: 130% *VREF. |

MFR_OVP_NOCP_SET (D5h)

El comando MFR_OVP_SET establece la respuesta tanto para el voltade salida OVP como para el voltade entrada OVP.

Bits | nombre | acceso | comportamiento | Por defecto | descripción |

[7:4] | Reservado. | 0000 | |||

[3] | DELAY_NOCP (D400) | R /w |

En vivo |

0 | 0: 100ns retraso después NOCP ; 1: 200ns de retraso después NOCP |

[2] |

NOCP | R /w |

En vivo |

0 | 0: set NOCP to -10A ; 1: set NOCP A -15A. |

[1:0] |

VOUT_OV La respuesta |

R /w |

En vivo |

00 | 00: latch-off con tensión de salida discharge 01: latch-off sin descarga de tensión de salida en DCM 10: el hipo Con tensión de salida discharge 11: el hipo Sin tensión de salida Descarga en DCM |

MFR_OT_OC_SET (D6h)

El comando MFR_OT_OC_SET establece la respuesta para OCP (protección de sobrecorriente), así como la respuesta y la histéresespara OTP (protección de sobretemperatura).

Bits | nombre | acceso | comportamiento | Por defecto | descripción | |||

[7:4] | Reservado. | 0000 | ||||||

[3] | OC_response | R /w | En vivo | 00 | 0: latch-off, nunca vuelva a intentarlo; | 1: | reintentar | |

[2:1] | (en inglés) | R /w |

En vivo |

00 | 00: 20.C; 10: 30.C; | 01: 25. C ; 11: 35. C | ||

[0] |

ot_respuesta | R /w |

En vivo |

0 | 0: latch-off, never reintentar 1: reintentar después de que las gotas de la temperatura cerca |

el |

valor set |

Por bit[2:1] |

MFR_OC_PHASE_SET (D7h)

El comando MFR_OC_PHASE_LIMIT establece el límite de corriente del valle para el inductor de cada fase.

Bits | nombre | acceso | comportamiento | Por defecto | descripción |

[7:5] | Reservado. | 000 | |||

[4:0] | OC_limit | R /w |

En vivo |

10100 | Current Límite. 1,5a /LSB, [00000] = 0A. |

MFR_HICCUP_ITV_SET (D8h)

El comando MFR_HICCUP_ITV_SET establece el intervalo de hipo durante los eventos OCP (overcurrent Protection).

| Bits | nombre | acceso | comportamiento | Por defecto | descripción |

[7:6] | Reservado. | 00 | |||

[5:0] |

Hiccup_itv |

R /w |

En vivo |

000000 | La falla del OC El,, o el,, interval Tiempo. 000000:4ms 1LSB = 4ms |

MFR_UVP_PGOOD_ON_LIMIT (D9h)

Bits | nombre | acceso | comportamiento | Por defecto | descripción |

[7:4] | Reservado. | 0000 | |||

[3:2] |

uv_o |

R /w |

En vivo |

00 | El conjunto el UVP Umbral. cuando FB Las gotas abajo el UV_TH Nivel, it enters UVP. 00: 69% * VREF; 01 % : 74% * VREF; 10: 79% * VREF; 11: 84% * VREF. |

[1:0] |

PG_ON |

R /w |

En vivo |

00 | Establece la entrada OVP Umbral. 00: 90% * VREF; 01: 92,5% * VREF 10: 95% * VREF; 11: 97.5% * VREF |

MFR_FB_STEP (DAh)

Bits | nombre | acceso | comportamiento | Por defecto | descripción |

[7:4] | Reservado. | 0000 | |||

[3:0] | FB_step | R /w | En vivo | 0000 | 0000: 5µs/mV; 1LSB = 1µs/mV |

MFR_LOW_POWER (en inglés) (E5h)

Bits | nombre | acceso | comportamiento | Por defecto | descripción |

[7:2] | Reservado. | 000000 | |||

[1:0] |

LP_PS# |

R /w |

En vivo |

00 | 11: el modo de baja potencia está activado cuando PS#es Bajos y discapacitados cuando PS# is high Otros: Aoto Fase fase sheding (en inglés) |

MFR_CTRL (EAh)

Bits | nombre | acceso | comportamiento | Por defecto | descripción |

[15:11] | Reservado. | r | En vivo | 00000 | For fabricante Use solamente. |

[10] | Total_OC_ hiccup_interv al |

R /w |

En vivo |

0 | Elige si el intervalo durante el OCP hipo puede ser Cambiado a través del registro D8h. 0: OCP fijo Intervalo de hipo 1: OCP ajustable Intervalo de hipo |

[9] |

OSM |

R /w |

En vivo |

0 | Activa o desactiva el salida Modo de hundimiento (OSM) Función. 0: habilitar el fregadero de salida modo (OSM) 1: deshabilitar OSM |

[8] | Reservado. | r | En vivo | 0 | |

[7] | autofase | R /w | En vivo | 0 | 0: deshabilitar 1: habilitar |

[6:4] | Phase_count | R /w | En vivo | 000 | Establecer el conteo of phase |

[3] | Gestión de la fase | R /w | En vivo | 1 | 0: monofásico 1: multifase |

[2:0] | Reservado. | r | En vivo | 000 | For fabricante Use solamente. |

Terreno recomendado Patrón patrón

Precauciones de soldadura y almacenamiento

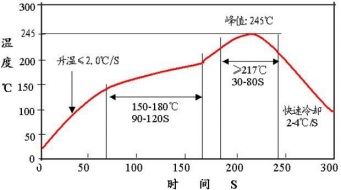

Perfil de soldadura por refrecomendado

Precaución:

1. Debido al gran tamaño del módulo, por favor no coloque el módulo debajo de la placa para la soldadura por reflujo para evitar que se caiga

2. Para los productos a granel y los que han sido sacados de su embalaje original, deben almacenarse en un desecador (con una humedad relativa inferior al 10% en su interior). En el caso de los productos que aún estén en su envase original, también se almacenarán en un desecador siempre que sea posible.

3. Antes de montar en la placa, es necesario seguir estrictamente las condiciones de cocción para secar las muestras: hornear a 125°C durante más de 48 horas, y controlar la temperatura de soldadura por refrefdentro de 245°

Modelo de producto | entrada | salida | paquete | grado | Rango de temperatura (temperatura de la caja) | embalaje |

FHM3695-25IV#PBF | 4~16V | 0,6 ~5..5V | LGA (sin plomo) | Grado Industrial | -40-125℃ | La bandeja |

FHM3695-25MV#PBF | 4~16V | 0,6 ~5..5V | LGA (sin plomo) | Grado militar General | 55-125℃ | La bandeja |

| El artículo | descripción | Carrete y la bandeja | PC/ rollo | G.W | N.W | QTY/ cartón | Tamaño del paquete |

FHM3695-25 | Entrada 4V-16V, salida 0.6V-5.5V DC/DC integrada Convertibuck ajustmolde. abajo Módulo de potencia, Hasta un 95% de eficiencia |

| 500pcs | 1.28kgs | 0.84kgs | 500pcs | 210*210*50mm |

Descubra todas las especificaciones técnicas descargando hoy mismo la hoja de datos.

| Número de pieza |

Corriente de salida

(A) |

Tensión de entrada

(V) |

Tensión de salida

(V) |

Dimensiones (mm) |

máximo

Efficienc |

Fábrica de paquetes

La cantidad |

La huella 3D | Hoja de datos | muestra |

| UDM2520I | 0.6A | 2.3V ~ 5.5V | 0.8V~3.3V | 2.5mm × 2mm x 1.1mm | 94% | 3,000pcs |  |

|

|

| UDM22006 | 0.6A | 2.3V~5.5V | 1.2V~3.3V | 2.5mm x 2mm x 1.1mm | 95% | 3,000pcs |  |

|

|

| UDM22010 | 1A | 2.3V ~ 5.5V | 1.2V ~ 3.3V | 2.5mm x 2mm x 1.1mm | 95% | 3,000pcs |  |

|

|

| UDM82821adj | 1A | 2.5V~5.5V | 0.8V~4V | 2.5mm × 2mm x 1.1mm | 95% | 3,000pcs |  |

|

|

| UDM82821 | 1.2A | 2.3V~5.5V | 1.2V~3.3V | 2.5mm × 2mm x 1.1mm | 95% | 3,000pcs |  |

|

|

| UDM2826I | 1.5A | 2.7V ~ 5.5V | 1V ~ 3.3V | 2.8mm × 2.6mm x 1.1mm | 93% | 3,000pcs |  |

|

|

| UDM3606 | 0.6A | 4.5V-18V | 0.6V-5.5V | 5mm×3.2mm×2.2mm | 95% | 3,000pcs |  |

|

|

| UDM3506 | 0.6A | 4.7V-36V | 0.8V | 5mm×3.2mm×2.2mm | 82% | 3,000pcs |  |

|

|

| UDM3610 | 1.2A | 4.5V~18V | 0.6V~5.5V | 5mm×3.2mm×2.2mm | 95% | 3,000pcs |  |

|

|

| UDM92403 | 0.3A | 0.7V~5.5V | 1.8V~5.5V | 2.5mm×2mm x 1.1mm | 93% | 3,000pcs |  |

|

|

| UDM81256 | 1A | 2.5V ~ 5.5V | 5V | 2.8mm×2.6mm×1.35mm(1.1mm) | 95% | 3,000pcs |  |

|

|

| FHT4644 | 4A | 4.0V ~ 15V | 0.8V ~ 5.5V | 9mm x 15mm x 4.32mm | 92% | 500pcs |  |

|

|

| FHT4644H | 4A | 4.0V ~14V | 0.6V ~ 5.5V | 9mmx15mmx4.32mm | 92% | 500pcs |  |

|

|

| FHT4644C/D | 4A | 4.5V-14V | 0.6V-5.5V | 9mmx15mmx4.32mm | 92% | 500pcs |  |

|

|

| FHT4644F | 4A | 4.5V ~ 16V | 0.6V ~ 5.5V | 9.0mmx15mmx4.32mm | 92% | 500pcs |  |

|

|

| FHT4644L | 4A | 4.0V ~15V | 0.8V ~ 5.5V | 9mmx15mmx1.82mm | 92% | 500pcs |  |

|

|

| FHT4630 | 18A+18A | 4.5V~15V | 0.6V ~ 1.8V | 16mm × 16mm × 5.01mm | 94% | 500pcs |  |

|

|

| FHT3860 | 6A | 2.3V-5.5V | 0.5V-3.3V | 4mm x 6mm x 1.6mm | 94% | 500pcs |  |

|

|

| FHM3695-25 | 20A | 4V-16V | 0.6V-5.5V | 10mm × 12mm ×4.32mm | 95% | 500pcs |  |

|

|

| FHT4623 | 3A | 4.2V-20V | 0.6V-5.5V | 6.75mm x 6.75mm x 2.95mm | 95% | 500pcs |  |

|

|

| MPPM8070 | 2A | 4.5V-18V | 0.6V-15V | 8mm×7mm × 4.32(2.5mm) | 93% | 500pcs |  |

|

|

| FHT4618 | 6A | 4.5V-24V | 0.6V-5.5V | 15mm×9mm×4.32mm | 95% | 500pcs |  |

|

|

| FHT23030 | 3A | 4.5V-17V | 0.9V-6V | 3mm×2.8mm×1.4mm | 94% | 500pcs |  |

|

|

| FHT3550 | 5A | 3.5V-40V | 1.0V-12.0V | 12mm x 12mm x 4.32mm | 95% | 500pcs |  |

|

|

| FHT8027C | 4A | 5V-60V | 2.5V-24V | 15mm×15mm×4.32mm | 95% | 500pcs |  |

|